# **ANALOG DEVICES** 6.2 GHz Fractional-N Frequency Synthesizer

### **Data Sheet**

# ADF4156

#### FEATURES

RF bandwidth to 6.2 GHz 2.7 V to 3.3 V power supply Separate V<sub>P</sub> pin allows extended tuning voltage Programmable fractional modulus Programmable charge-pump currents 3-wire serial interface Digital lock detect Power-down mode Pin compatible with ADF4110/ADF4111/ADF4112/ADF4113, ADF4106, ADF4153, and ADF4154 frequency synthesizers Programmable RF output phase Loop filter design possible with ADIsimPLL

#### **APPLICATIONS**

CATV equipment Base stations for mobile radio (WiMAX, GSM, PCS, DCS, SuperCell 3G, CDMA, WCDMA) Wireless handsets (GSM, PCS, DCS, CDMA, WCDMA) Wireless LANs, PMR Communications test equipment

Cycle slip reduction for faster lock times

#### **GENERAL DESCRIPTION**

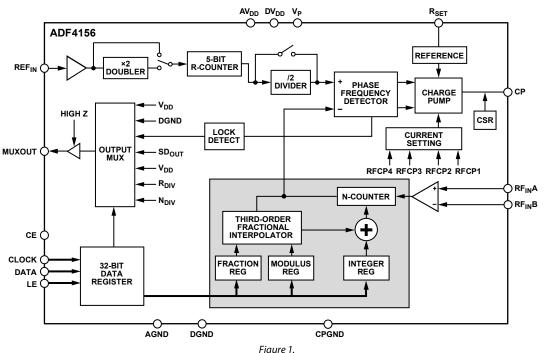

The ADF4156 is a 6.2 GHz fractional-N frequency synthesizer that implements local oscillators in the upconversion and downconversion sections of wireless receivers and transmitters. It consists of a low noise digital phase frequency detector (PFD), a precision charge pump, and a programmable reference divider. There is a  $\Sigma$ - $\Delta$  based fractional interpolator to allow programmable fractional-N division. The INT, FRAC, and MOD registers define an overall N divider (N = (INT + (FRAC/MOD))). The RF output phase is programmable for applications that require a particular phase relationship between the output and the reference. The ADF4156 also features cycle slip reduction circuitry, leading to faster lock times without the need for modifications to the loop filter.

Control of all on-chip registers is via a simple 3-wire interface. The device operates with a power supply ranging from 2.7 V to 3.3 V and can be powered down when not in use.

#### FUNCTIONAL BLOCK DIAGRAM

#### Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2006-2012 Analog Devices, Inc. All rights reserved.

### **TABLE OF CONTENTS**

### **REVISION HISTORY**

| 3/12—Rev. C to Rev. D                                          |

|----------------------------------------------------------------|

| Changes to Table 1 3                                           |

| Changes to Ordering Guide 22                                   |

| 9/11—Rev. B to Rev. C                                          |

| Changes to Noise Characteristics Parameter 3                   |

| 4/11—Rev. A to Rev. B                                          |

| Changes to Product Title, Features Section and General         |

| Description Section 1                                          |

| Changes to RF Input Frequency $RF_{\rm IN}$ Parameter, Table 1 |

| Changes to Figure 4 and Table 5 6                              |

| 5/09—Rev. 0 to Rev. A                                          |

| Added Low Power Sleep Mode Parameter and Changes to            |

| Endnote 4, Table 1 3                                           |

| Change to Figure 9 Caption7                                    |

| Change to Program Modes Section9                               |

| Changes to Figure 16 10                                        |

|                                                                |

| Register Maps 10                                     |

|------------------------------------------------------|

| FRAC/INT Register, R011                              |

| Phase Register, R1 12                                |

| MOD/R Register, R2 13                                |

| Function Register, R315                              |

| CLK DIV Register, R4 16                              |

| Reserved Bits16                                      |

| Initialization Sequence16                            |

| RF Synthesizer: A Worked Example17                   |

| Modulus17                                            |

| Reference Doubler and Reference Divider              |

| 12-Bit Programmable Modulus17                        |

| Fast Lock Times with the ADF4156 17                  |

| Spur Mechanisms 19                                   |

| Spur Consistency and Fractional Spur Optimization 19 |

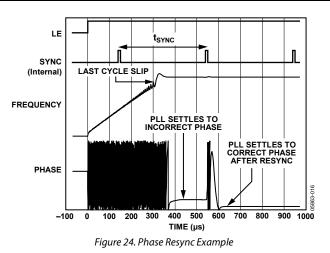

| Phase Resync                                         |

| Low Frequency Applications 20                        |

| Filter Design—ADIsimPLL                              |

| Interfacing 21                                       |

| PCB Design Guidelines for Chip Scale Package         |

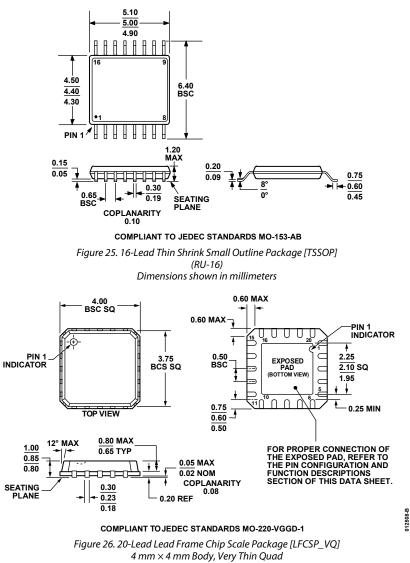

| Outline Dimensions                                   |

| Ordering Guide 22                                    |

| Changes to Figure 17 11                                     |

|-------------------------------------------------------------|

| Changes to CSR Enable Section 13                            |

| Changes to Figure 19 14                                     |

| Changes to Function Register, R3 Section and Figure 20 15   |

| Changes to 12-Bit Clock Divider Value Section, to           |

| Clock Divider Mode Section, and to Figure 21 16             |

| Changes to Reference Doubler and Reference Divider Section  |

| and to Fast Lock Times with the ADF4156 Section 17          |

| Added Figure 22 and Figure 23; Renumbered Sequentially 19   |

| Change to Phase Resync Section 20                           |

| Changes to Interfacing Section and to PCB Design Guidelines |

| for Chip Scale Package Section 21                           |

| Changes to Outline Dimensions 23                            |

| Changes to Ordering Guide 23                                |

|                                                             |

5/06—Revision 0: Initial Version

### **SPECIFICATIONS**

$AV_{DD} = DV_{DD} = 2.7 V$  to 3.3 V,  $V_P = AV_{DD}$  to 5.5 V, AGND = DGND = 0 V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , dBm referred to 50  $\Omega$ , unless otherwise noted.

| Parameter                                                        | <b>B</b> Version      | Unit          | Test Conditions/Comments <sup>1</sup>                                                    |

|------------------------------------------------------------------|-----------------------|---------------|------------------------------------------------------------------------------------------|

| RF CHARACTERISTICS                                               |                       |               |                                                                                          |

| RF Input Frequency (RF <sub>IN</sub> )                           | 0.5/6.2               | GHz min/max   | -10 dBm min to 0 dBm max. For lower frequencies, ensure slew rate (SR) > 400 V/µs.       |

| REFERENCE CHARACTERISTICS                                        |                       |               |                                                                                          |

| REF <sub>IN</sub> Input Frequency                                | 10/250                | MHz min/max   | For f < 10 MHz, use a dc-coupled CMOS-compatible square wave, slew rate > 25 V/ $\mu$ s. |

| REF <sub>IN</sub> Input Sensitivity                              | 0.4/AV <sub>DD</sub>  | V p-p min/max | Biased at AV <sub>DD</sub> /2. <sup>2</sup>                                              |

| REF <sub>IN</sub> Input Capacitance                              | 10                    | pF max        |                                                                                          |

| REF <sub>IN</sub> Input Current                                  | ±100                  | μA max        |                                                                                          |

| PHASE DETECTOR                                                   |                       |               |                                                                                          |

| Phase Detector Frequency <sup>3</sup>                            | 32                    | MHz max       |                                                                                          |

| CHARGE PUMP                                                      |                       |               |                                                                                          |

| I <sub>CP</sub> Sink/Source                                      |                       |               | Programmable.                                                                            |

| High Value                                                       | 5                     | mA typ        | With $R_{\text{SET}} = 5.1 \text{ k}\Omega$ .                                            |

| Low Value                                                        | 312.5                 | μA typ        |                                                                                          |

| Absolute Accuracy                                                | 2.5                   | % typ         | With $R_{\text{SET}} = 5.1 \text{ k}\Omega$ .                                            |

| R <sub>SET</sub> Range                                           | 2.7/10                | kΩ min/max    |                                                                                          |

| I <sub>CP</sub> Three-State Leakage Current                      | 1                     | nA typ        | Sink and source current.                                                                 |

| Matching                                                         | 2                     | % typ         | $0.5 V < V_{CP} < V_{P} - 0.5.$                                                          |

| ICP VS. VCP                                                      | 2                     | % typ         | $0.5 V < V_{CP} < V_{P} - 0.5.$                                                          |

| I <sub>CP</sub> vs. Temperature                                  | 2                     | % typ         | $V_{CP} = V_P/2.$                                                                        |

| LOGIC INPUTS                                                     |                       |               |                                                                                          |

| V <sub>INH</sub> , Input High Voltage                            | 1.4                   | V min         |                                                                                          |

| V <sub>INL</sub> , Input Low Voltage                             | 0.6                   | V max         |                                                                                          |

|                                                                  | ±1                    | μA max        |                                                                                          |

| C <sub>IN</sub> , Input Capacitance                              | 10                    | pF max        |                                                                                          |

| LOGIC OUTPUTS                                                    |                       |               |                                                                                          |

| V <sub>он</sub> , Output High Voltage                            | 1.4                   | V min         | Open-drain output chosen; 1 k $\Omega$ pull-up to 1.8 V.                                 |

| V <sub>он</sub> , Output High Voltage                            | $V_{\text{DD}} - 0.4$ | V min         | CMOS output chosen.                                                                      |

| I <sub>oH</sub> , Output High Current                            | 100                   | μA max        |                                                                                          |

| Vol, Output Low Voltage                                          | 0.4                   | V max         | $I_{OL} = 500 \ \mu A.$                                                                  |

| POWER SUPPLIES                                                   |                       |               |                                                                                          |

| AV <sub>DD</sub>                                                 | 2.7/3.3               | V min/max     |                                                                                          |

| DV <sub>DD</sub>                                                 | AV <sub>DD</sub>      |               |                                                                                          |

| VP                                                               | AV <sub>DD</sub> /5.5 | V min/max     |                                                                                          |

| I <sub>DD</sub>                                                  | 32                    | mA max        | 26 mA typical.                                                                           |

| Low Power Sleep Mode                                             | 1                     | μA typ        |                                                                                          |

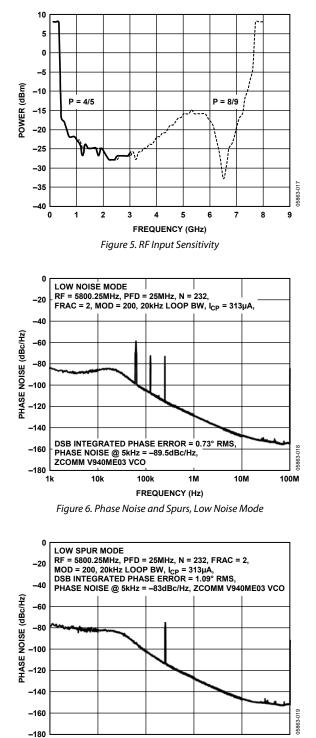

| NOISE CHARACTERISTICS                                            |                       |               |                                                                                          |

| Normalized Phase Noise Floor (PN <sub>SYNTH</sub> ) <sup>4</sup> | -220                  | dBc/Hz typ    | PLL loop BW = 500 kHz. Measured at 100 kHz offset.                                       |

| Normalized 1/f Noise (PN <sub>1_f</sub> ) <sup>5</sup>           | -110                  | dBc/Hz typ    | 10 kHz offset; normalized to 1 GHz.                                                      |

| Phase Noise Performance <sup>6</sup>                             |                       |               | @ VCO output.                                                                            |

| 5800 MHz Output <sup>7</sup>                                     | -89                   | dBc/Hz typ    | @ 5 kHz offset, 25 MHz PFD frequency.                                                    |

$^1$  Operating temperature for B version:  $-40^\circ\text{C}$  to  $+85^\circ\text{C}.$   $^2$  AC coupling ensures AV\_DD/2 bias.

<sup>3</sup> Guaranteed by design. Sample tested to ensure compliance.

<sup>4</sup> The synthesizer phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20 log(N) (where N is the N divider value) and 10 log( $F_{PFD}$ ). PN<sub>SYNTH</sub> = PN<sub>TOT</sub> - 10 log( $F_{PFD}$ ) - 20 log(N).

<sup>5</sup> The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency,  $F_{RF}$ , and at a frequency offset f is given by PN = PN<sub>1.f</sub> + 10 log(10 kHz/f) + 20 log( $F_{RF}$ /1 GHz). Both the normalized phase noise floor and flicker noise are modeled in ADIsimPLL. <sup>6</sup> The phase noise is measured with the EV-ADF4156SD1Z evaluation board and the Agilent E5500 phase noise system.

<sup>7</sup> f<sub>REFIN</sub> = 100 MHz, f<sub>PFD</sub> = 25 MHz, offset frequency = 5 kHz, RF<sub>OUT</sub> = 5800 MHz, N = 232, loop bandwidth = 20 kHz, l<sub>CP</sub> = 313 µA, and lowest noise mode.

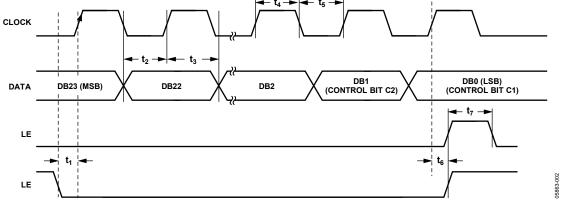

### TIMING SPECIFICATIONS

$AV_{DD} = DV_{DD} = 2.7 V$  to 3.3 V,  $V_P = AV_{DD}$  to 5.5 V, AGND = DGND = 0 V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , dBm referred to 50  $\Omega$ , unless otherwise noted.

| Table 2.       |                                                           |        |                          |

|----------------|-----------------------------------------------------------|--------|--------------------------|

| Parameter      | Limit at T <sub>MIN</sub> to T <sub>MAX</sub> (B Version) | Unit   | Test Conditions/Comments |

| t1             | 20                                                        | ns min | LE setup time            |

| t <sub>2</sub> | 10                                                        | ns min | DATA to CLOCK setup time |

| t <sub>3</sub> | 10                                                        | ns min | DATA to CLOCK hold time  |

| t4             | 25                                                        | ns min | CLOCK high duration      |

| t <sub>5</sub> | 25                                                        | ns min | CLOCK low duration       |

| t <sub>6</sub> | 10                                                        | ns min | CLOCK to LE setup time   |

| t <sub>7</sub> | 20                                                        | ns min | LE pulse width           |

#### Timing Diagram

Figure 2. Timing Diagram

### ABSOLUTE MAXIMUM RATINGS

$T_{\rm A} = 25^{\circ}C, \ GND = AGND = DGND = 0 \ V, \ V_{\rm DD} = AV_{\rm DD} = DV_{\rm DD},$  unless otherwise noted.

#### Table 3.

| Parameter                          | Rating                            |

|------------------------------------|-----------------------------------|

| V <sub>DD</sub> to GND             | -0.3 V to +4 V                    |

| V <sub>DD</sub> to V <sub>DD</sub> | –0.3 V to +0.3 V                  |

| V <sub>P</sub> to GND              | –0.3 V to +5.8 V                  |

| $V_P$ to $V_{DD}$                  | –0.3 V to +5.8 V                  |

| Digital I/O Voltage to GND         | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Analog I/O Voltage to GND          | -0.3 V to V <sub>DD</sub> + 0.3 V |

| REFIN, RFIN tO GND                 | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Operating Temperature Range        |                                   |

| Industrial (B Version)             | -40°C to +85°C                    |

| Storage Temperature Range          | –65°C to +125°C                   |

| Maximum Junction Temperature       | 150°C                             |

| Reflow Soldering                   |                                   |

| Peak Temperature                   | 260°C                             |

| Time at Peak Temperature           | 40 sec                            |

| Maximum Junction Temperature       | 150°C                             |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device is a high performance RF integrated circuit with an ESD rating of <2 kV, and it is ESD sensitive. Proper precautions should be taken for handling and assembly.

#### THERMAL IMPEDANCE

#### Table 4. Thermal Impedance

| Package Type               | Αιθ  | Unit |

|----------------------------|------|------|

| TSSOP                      | 112  | °C/W |

| LFCSP_VQ (Paddle Soldered) | 30.4 | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

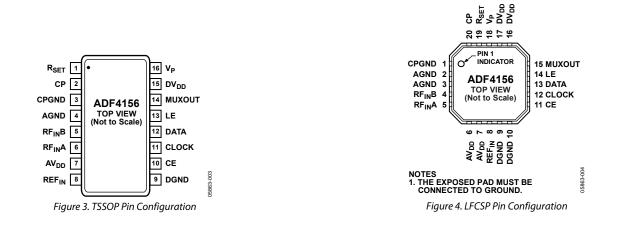

### **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

#### Table 5. Pin Function Descriptions

| Pin   | No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |                                                                                                                                                                                                                                             |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | LFCSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Mnemonic           | Description                                                                                                                                                                                                                                 |

| 1     | 19RsetConnecting a resistor between trelationship between $l_{CP}$ and $R_{SE}$ $I_{CPmax} = \frac{25.5}{R_{SET}}$ $V_{CPmax} = \frac{25.5}{R_{SET}}$ 20CPCharge-Pump Output. When en<br>the external VCO.1CPGNDCharge-Pump Ground. This is the groun<br>42, 3AGNDAnalog Ground. This is the groun<br>44RFINBComplementary Input to the RF<br>capacitor, typically 100 pF.5RFINAInput to the RF Prescaler. This sn<br>6, 76, 7AV_DDPositive Power Supply for the RF<br>placed as close as possible to this<br>three-state mode.8REFINReference Input. This is a CMOS<br>of 100 k $\Omega$ . This input can be driv<br>three-state mode.12CLOCKSerial Clock Input. This serial clo<br>into the shift register on the CLO<br>into the shift register on the CLO<br>five latches. The control bits are<br>five latches. The control bits are<br>placed as close as possible to this<br>five latches. The control bits are<br>five latches. The control bits are<br>five latches. The control bits are<br>placed as close as possible to this<br>five latches. The control bits are<br>five latches. The control bits are<br>five latches. The control bits are<br>placed as close as possible to this<br>five latches. The control bits are<br>five latches. The control bits are<br>five latches. The control bits are<br>placed as close as possible to this<br>five latches. The placed as close as possible to this<br>five latches. The placed as close as possible to this<br>five latches. The placed as close as possible to this<br>placed |                    | Connecting a resistor between this pin and ground sets the maximum charge-pump output current. The relationship between $I_{CP}$ and $R_{SET}$ is                                                                                           |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | $I_{CPmax} = \frac{25.5}{R_{SET}}$                                                                                                                                                                                                          |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | where $R_{SET} = 5.1 \text{ k}\Omega$ and $I_{CPmax} = 5 \text{ mA}$ .                                                                                                                                                                      |

| 2     | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | СР                 | Charge-Pump Output. When enabled, this pin provides $\pm I_{CP}$ to the external loop filter, which in turn drives the external VCO.                                                                                                        |

| 3     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CPGND              | Charge-Pump Ground. This is the ground return path for the charge pump.                                                                                                                                                                     |

| 4     | 2, 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | AGND               | Analog Ground. This is the ground return path of the prescaler.                                                                                                                                                                             |

| 5     | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RFıℕB              | Complementary Input to the RF Prescaler. Decouple this point to the ground plane with a small bypass capacitor, typically 100 pF.                                                                                                           |

| 6     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RF <sub>IN</sub> A | Input to the RF Prescaler. This small-signal input is normally ac-coupled from the VCO.                                                                                                                                                     |

| 7     | relationship between $I_{CP}$ and $R_{SE}$ $I_{CPmax} = \frac{25.5}{R_{SET}}$ 20CP1CPGND1CPGND2,3AGND4RFINB2,3AGND4RFINB5RFINA6,7AV_DD9,10DGND11CE12CLOCK13DATA14LE15MUXOUT14LE15MUXOUT14LE15MUXOUT16,17DV_DD16,17DV_DD16,17DV_DD17Dositive Power Supply for the D18VP18VP18VP18VP18VP18VP18VP18VP1910DSI10DOS11CE12CLOCK13DATA14LE15MUXOUT16,17DV_DD17Positive Power Supply for the D18VP18VP18VP18VP18VP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    | Positive Power Supply for the RF Section. Decoupling capacitors to the digital ground plane should be placed as close as possible to this pin. $AV_{DD}$ has a value of 3 V $\pm$ 10%. $AV_{DD}$ must have the same voltage as $DV_{DD}$ .  |

| 8     | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | REF <sub>IN</sub>  | Reference Input. This is a CMOS input with a nominal threshold of $V_{DD}/2$ and an equivalent input resistance of 100 k $\Omega$ . This input can be driven from a TTL or CMOS crystal oscillator, or it can be ac-coupled.                |

| 9     | 9, 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DGND               | Digital Ground.                                                                                                                                                                                                                             |

| 10    | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CE                 | Chip Enable. A logic low on this pin powers down the device and puts the charge-pump output into three-state mode.                                                                                                                          |

| 11    | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CLOCK              | Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the shift register on the CLOCK rising edge. This input is a high impedance CMOS input.                                |

| 12    | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DATA               | Serial Data Input. The serial data is loaded MSB first with the three LSBs serving as the control bits. This input is a high impedance CMOS input.                                                                                          |

| 13    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LE                 | Load Enable, CMOS Input. When LE is high, the data stored in the shift registers is loaded into one of the five latches. The control bits are used to select the latch.                                                                     |

| 14    | relationship between $I_{CP}$ and $R_{SET}$ $I_{CPmax} = \frac{25.5}{R_{SET}}$ 20CPCharge-Pump Output. When en<br>the external VCO.1CPGND2,3AGND4RF <sub>IN</sub> B2,3AGND4RF <sub>IN</sub> B5RF <sub>IN</sub> A6,7AV <sub>DD</sub> 9,10DGND11CE12CLOCK13DATA14LE15MUXOUT14LE15MUXOUT14LE15MUXOUT14LE15MUXOUT16,17DV <sub>DD</sub> 16,17DV <sub>DD</sub> 17Positive Power Supply for the Diplaced as close as possible to this<br>placed as close as possible to this<br>three-state mode.12CLOCK13DATA14LE15MUXOUT16,17DV <sub>DD</sub> 18VP18VP18VP18VP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    | Multiplexer Output. This multiplexer output allows either the RF lock detect, the scaled RF, or the scaled reference frequency to be accessed externally.                                                                                   |

| 15    | 16, 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    | Positive Power Supply for the Digital Section. Decoupling capacitors to the digital ground plane should be placed as close as possible to this pin. $DV_{DD}$ has a value of 3 V ± 10%. $DV_{DD}$ must have the same voltage as $AV_{DD}$ . |

| 16    | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VP                 | Charge-Pump Power Supply. This should be greater than or equal to V <sub>DD</sub> . In systems where V <sub>DD</sub> is 3 V, it can be set to 5.5 V and used to drive a VCO with a tuning range of up to 5.5 V.                             |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EPAD               | The exposed pad must be connected to ground.                                                                                                                                                                                                |

### **TYPICAL PERFORMANCE CHARACTERISTICS**

PFD = 25 MHz, loop bandwidth = 20 kHz, reference = 100 MHz,  $I_{CP} = 313 \mu A$ , phase noise measurements taken on the Agilent E5500 phase noise system.

FREQUENCY (Hz) Figure 7. Phase Noise and Spurs, Low Spur Mode (Note that Fractional Spurs Are Removed and Only the Integer Boundary Spur Remains in Low Spur Mode)

1M

10M

100M

100k

10k

1k

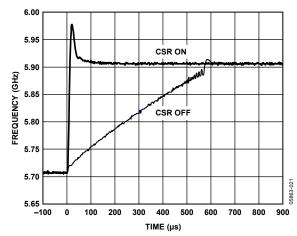

Figure 8. Lock Time for 200 MHz Jump, from 5705 MHz to 5905 MHz, with CSR On and Off

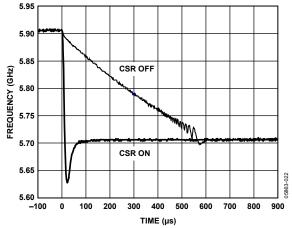

Figure 9. Lock Time for 200 MHz Jump, from 5905 MHz to 5705 MHz, with CSR On and Off

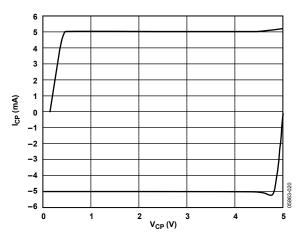

Figure 10. Charge-Pump Output Characteristics

# CIRCUIT DESCRIPTION

#### **REFERENCE INPUT SECTION**

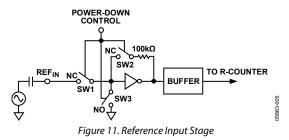

The reference input stage is shown in Figure 11. While the device is operating, SW1 and SW2 are usually closed switches and SW3 is open. When a power-down is initiated, SW3 is closed and SW1 and SW2 are opened. This ensures that the REF<sub>IN</sub> pin is not loaded while the device is powered down.

#### **RF INPUT STAGE**

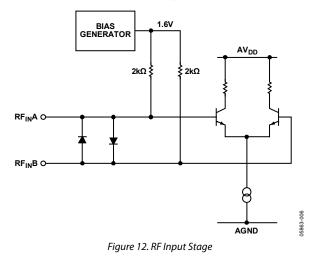

The RF input stage is shown in Figure 12. It is followed by a two-stage limiting amplifier to generate the current-mode logic (CML) clock levels needed for the prescaler.

#### **RF INT DIVIDER**

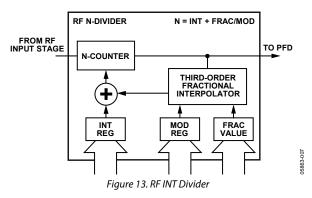

The RF INT counter allows a division ratio in the PLL feedback counter. Division ratios from 23 to 4095 are allowed.

#### INT, FRAC, MOD, AND R RELATIONSHIP

The INT, FRAC, and MOD values, in conjunction with the R-counter, enable generating output frequencies that are spaced by fractions of the phase frequency detector (PFD). See the RF Synthesizer: A Worked Example section for more information. The RF VCO frequency ( $RF_{OUT}$ ) equation is

$$RF_{OUT} = F_{PFD} \times (INT + (FRAC/MOD))$$

(1)

where *RF*<sub>OUT</sub> is the output frequency of an external voltagecontrolled oscillator (VCO).

$$F_{PFD} = REF_{IN} \times [(1+D)/(R \times (1+T))]$$

(2)

where:

*REF*<sub>IN</sub> is the reference input frequency.

D is the REF<sub>IN</sub> doubler bit.

*T* is the  $\text{REF}_{IN}$  divide-by-2 bit (0 or 1).

*R* is the preset divide ratio of the binary 5-bit programmable reference counter (1 to 32).

*INT* is the preset divide ratio of the binary 12-bit counter (23 to 4095).

MOD is the preset fractional modulus (2 to 4095).

FRAC is the numerator of the fractional division (0 to MOD - 1).

#### **RF R-COUNTER**

The 5-bit RF R-counter allows the input reference frequency  $(REF_{IN})$  to be divided down to produce the reference clock to the PFD. Division ratios from 1 to 32 are allowed.

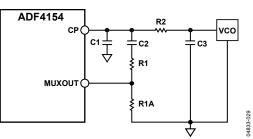

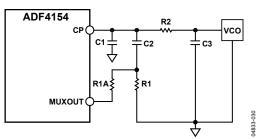

# PHASE FREQUENCY DETECTOR (PFD) AND CHARGE PUMP

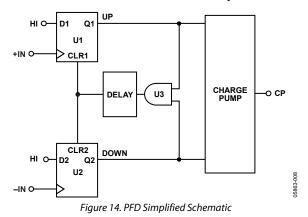

The PFD takes inputs from the R-counter and N-counter and produces an output proportional to the phase and frequency difference between them. Figure 14 is a simplified schematic of the phase frequency detector. The PFD includes a fixed-delay element that sets the width of the antibacklash pulse, which is typically 3 ns. This pulse ensures that there is no dead zone in the PFD transfer function and results in a consistent reference spur level.

#### MUXOUT AND LOCK DETECT

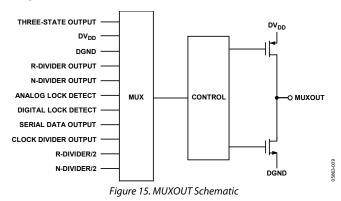

The output multiplexer on the ADF4156 allows the user to access various internal points on the chip. The state of MUXOUT is controlled by M4, M3, M2, and M1 (for details, see Figure 16). Figure 15 shows the MUXOUT section in block diagram form.

#### **INPUT SHIFT REGISTERS**

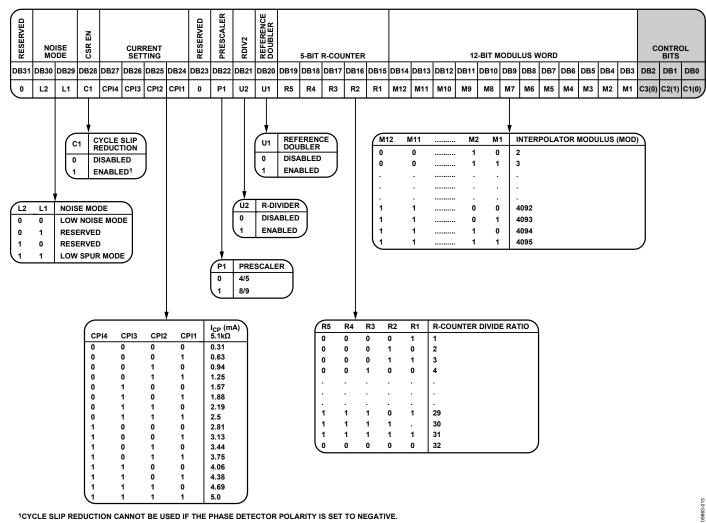

The ADF4156 digital section includes a 5-bit RF R-counter, a 12-bit RF N-counter, a 12-bit FRAC counter, and a 12-bit modulus counter. Data is clocked into the 32-bit shift register on each rising edge of CLOCK. The data is clocked in MSB first. Data is transferred from the shift register to one of five latches on the rising edge of LE. The destination latch is determined by the state of the three control bits (C3, C2, and C1) in the shift register. These bits are the three LSBs (DB2, DB1, and DB0), as shown in Figure 2. The truth table for these bits is shown in Table 6. Figure 16 shows a summary of how the latches are programmed.

#### **PROGRAM MODES**

Table 6 and Figure 16 through Figure 21 show how to set up the program modes in the ADF4156.

Several settings in the ADF4156 are double buffered, including the modulus value, phase value, R-counter value, reference doubler, reference divide-by-2, and current setting. This means that two events must occur before the part can use a new value for any of the double buffered settings. The new value must first be latched into the device by writing to the appropriate register, and then a new write must be performed on Register R0. For example, after the modulus value is updated, Register R0 must be written to in order to ensure that the modulus value is loaded correctly.

#### Table 6. C3, C2, and C1 Truth Table

|    | Control                  | Bits |             |  |

|----|--------------------------|------|-------------|--|

| C3 | 0 0<br>0 1<br>1 0<br>1 1 |      | Register    |  |

| 0  | 0                        | 0    | Register R0 |  |

| 0  | 0                        | 1    | Register R1 |  |

| 0  | 1                        | 0    | Register R2 |  |

| 0  | 1                        | 1    | Register R3 |  |

| 1  | 0                        | 0    | Register R4 |  |

1

Т

05863-010

### **REGISTER MAPS**

| RE-<br>SERVED | RE-<br>RVED MUXOUT CONTROL 12-BIT INTEGER VALUE (INT) |      |      |      |      |      |      |      |      | 12-BIT FRACTIONAL VALUE (FRAC) |      |      |      |      |      |      |      |      |      | CONTROL<br>BITS |      |     |     |     |     |     |     |     |       |       |       |

|---------------|-------------------------------------------------------|------|------|------|------|------|------|------|------|--------------------------------|------|------|------|------|------|------|------|------|------|-----------------|------|-----|-----|-----|-----|-----|-----|-----|-------|-------|-------|

| DB31          | DB30                                                  | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21                           | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11            | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2   | DB1   | DB0   |

| 0             | M4                                                    | М3   | M2   | M1   | N12  | N11  | N10  | N9   | N8   | N7                             | N6   | N5   | N4   | N3   | N2   | N1   | F12  | F11  | F10  | F9              | F8   | F7  | F6  | F5  | F4  | F3  | F2  | F1  | C3(0) | C2(0) | C1(0) |

#### PHASE REGISTER (R1) CONTROL BITS RESERVED 12-BIT PHASE VALUE (PHASE)<sup>1</sup> DB31 DB30 DB29 DB28 DB27 DB26 DB25 DB24 DB23 DB22 DB21 DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 P6 P5 P2 P1 C3(0) C2(0) C1(1) 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 P12 P11 P10 P9 **P**8 **P**7 P4 P3

|    |        | MOD/R REGISTER | (R2) |

|----|--------|----------------|------|

| ER | ц<br>Е |                |      |

| RESERVED |      | ISE  | CSR EN |      | CUR  | RENT<br>FING <sup>1</sup> |      | RESERVED | PRESCALER | RDIV21 | REFERENCE<br>DOUBLER <sup>1</sup> | 4    | 5-BIT F | R COU | NTER | I    |      |      |      | 12   | -BIT M | ODUL | .US W | ORD <sup>1</sup> |     |     |     |     | C     |       | DL    |

|----------|------|------|--------|------|------|---------------------------|------|----------|-----------|--------|-----------------------------------|------|---------|-------|------|------|------|------|------|------|--------|------|-------|------------------|-----|-----|-----|-----|-------|-------|-------|

| DB31     | DB30 | DB29 | DB28   | DB27 | DB26 | DB25                      | DB24 | DB23     | DB22      | DB21   | DB20                              | DB19 | DB18    | DB17  | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10   | DB9  | DB8   | DB7              | DB6 | DB5 | DB4 | DB3 | DB2   | DB1   | DB0   |

| Co       | L2   | L1   | C1     | CPI4 | CPI3 | CPI2                      | CPI1 | 0        | P1        | U2     | U1                                | R5   | R4      | R3    | R2   | R1   | M12  | M11  | M10  | М9   | M8     | M7   | M6    | M5               | M4  | М3  | M2  | M1  | C3(0) | C2(1) | C1(0) |

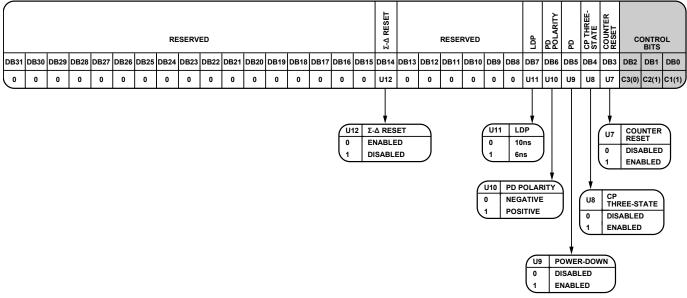

#### FUNCTION REGISTER (R3)

|    |         |      |      |      |      |      | RE   | SERVI | ED   |      |      |      |      |      |      |      | Σ-Δ RESET |      |      | RESEF | RVED |     |     | LDP | PD<br>POLARITY | PD  | CP THREE-<br>STATE | COUNTER<br>RESET | CC    | ONTRO<br>BITS | )L    |

|----|---------|------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|-----------|------|------|-------|------|-----|-----|-----|----------------|-----|--------------------|------------------|-------|---------------|-------|

| DB | 31 DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23  | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14      | DB13 | DB12 | DB11  | DB10 | DB9 | DB8 | DB7 | DB6            | DB5 | DB4                | DB3              | DB2   | DB1           | DB0   |

| Ū  | 0       | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | U12       | 0    | 0    | 0     | 0    | 0   | 0   | U7  | U6             | U5  | U4                 | U3               | C3(0) | C2(1)         | C1(1) |

#### CLK DIV REGISTER (R4)

| $\bigcap$ |      |      |      | RE   | SERV | ED   |      |      |      |      | CI<br>D<br>MO |      |      |      |      | 12-E |      | оск р | IVIDEF | R VALU | JE   |     |     |     |     | RESE | RVED |     | C     | ONTRO<br>BITS | эL    |

|-----------|------|------|------|------|------|------|------|------|------|------|---------------|------|------|------|------|------|------|-------|--------|--------|------|-----|-----|-----|-----|------|------|-----|-------|---------------|-------|

| DB31      | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20          | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13  | DB12   | DB11   | DB10 | DB9 | DB8 | DB7 | DB6 | DB5  | DB4  | DB3 | DB2   | DB1           | DB0   |

| O         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | M2            | M1   | D12  | D11  | D10  | D9   | D8   | D7    | D6     | D5     | D4   | D3  | D2  | D1  | 0   | 0    | 0    | 0   | C3(1) | C2(0)         | C1(0) |

<sup>1</sup>DOUBLE BUFFERED BIT.

Figure 16. Register Summary

5863-011

#### FRAC/INT REGISTER, RO

With the control bits (Bits[2:0]) of Register R0 set to 000, the on-chip FRAC/INT register is programmed. Figure 17 shows the input data format for programming this register.

#### 12-Bit Integer Value (INT)

These 12 bits control what is loaded as the INT value. This determines the overall feedback division factor. It is used in Equation 1 (see the INT, FRAC, MOD, and R Relationship section).

#### 12-Bit Fractional Value (FRAC)

These 12 bits control what is loaded as the FRAC value into the fractional interpolator. This is part of what determines the overall feedback division factor. It is also used in Equation 1. The FRAC value must be less than the value loaded into the MOD register.

#### Μυχουτ

The on-chip multiplexer is controlled by DB30, DB29, DB28, and DB27 on the ADF4156. See Figure 17 for the truth table.

| RE-<br>SERV                                                              | ED                                                                       | MU                                                                      | xou | т со                                                                                                   | NTF                                                                                    | ROL                                                                                                                   |                                                                                           |                                  |                                   |    | 12   | -BIT IN | TEGE | R VAL | UE (IN | IT)  |      |      |      |                                             |                                                  | 1:     | 2-BIT F                              | RAC                                         | TIONA | L VAL                                                    | .UE (F | RAC)  |      |       |     | C     | ONTR<br>BITS | OL   |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------|----|------|---------|------|-------|--------|------|------|------|------|---------------------------------------------|--------------------------------------------------|--------|--------------------------------------|---------------------------------------------|-------|----------------------------------------------------------|--------|-------|------|-------|-----|-------|--------------|------|

| DB3                                                                      | 1 [                                                                      | DB30                                                                    | DB2 | 29 DE                                                                                                  | 328                                                                                    | DB27                                                                                                                  | DB26                                                                                      | DB                               | 25 DE                             | 24 | DB23 | DB22    | DB21 | DB20  | DB19   | DB18 | DB17 | DB16 | DB15 | DB14                                        | DB13                                             | DB12   | DB11                                 | DB1                                         | 0 DB9 | DB8                                                      | DB7    | DB6   | DB5  | DB4   | DB3 | DB2   | DB1          | DBC  |

| 0                                                                        |                                                                          | M4                                                                      | M   | 3 N                                                                                                    | /12                                                                                    | M1                                                                                                                    | N12                                                                                       | N1                               | 11 N                              | 10 | N9   | N8      | N7   | N6    | N5     | N4   | N3   | N2   | N1   | F12                                         | F11                                              | F10    | F9                                   | F8                                          | F7    | F6                                                       | F5     | F4    | F3   | F2    | F1  | C3(0) | C2(0)        | C1(0 |